54ACT16833

54ACT16833 is DUAL 8-BIT TO 9-BIT PARITY BUS TRANSCEIVERS manufactured by Texas Instruments.

54ACT16833, 74ACT16833 DUAL 8-BIT TO 9-BIT PARITY BUS TRANSCEIVERS

SCAS166A

- JUNE 1990

- REVISED APRIL 1996

D Members of the Texas Instruments

Widebus ™ Family

D Inputs Are TTL-Voltage patible D Parity Error Flag With Parity

Generator/Checker

D Register for Storage of the Parity Error Flag D Flow-Through Architecture Optimizes

PCB Layout

D Distributed VCC and GND Pin Configuration

Minimizes High-Speed Switching Noise

D EPIC™ (Enhanced-Performance Implanted

CMOS) 1-µm Process

D 500-m A Typical Latch-Up Immunity at

125°C

D Package Options Include 300-mil Shrink

Small-Outline (DL) Packages Using 25-mil Center-to-Center Pin Spacings and 380-mil Fine-Pitch Ceramic Flat (WD) Packages Using 25-mil Center-to-Center Pin Spacings description

The ’ACT16833 consist of two noninverting 8-bit to 9-bit parity bus transceivers and are designed for munication between data buses. For each transceiver, when data is transmitted from the A bus to the B bus, an odd-parity bit is generated and output on the parity I/O pin (1PARITY or 2PARITY). When data is transmitted from the B bus to the A bus, 1PARITY or 2PARITY is configured as an input and bined with the B-input data to generate an active-low error flag if odd parity is not detected.

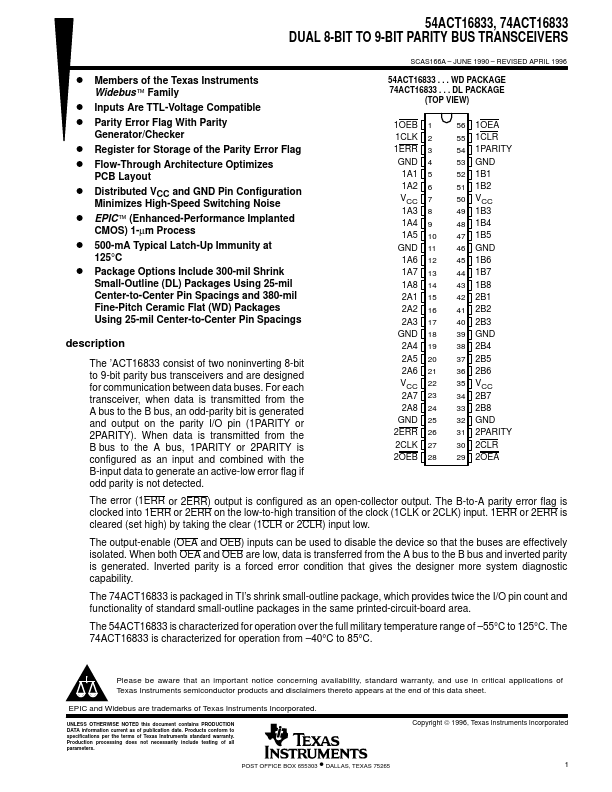

54ACT16833 . . . WD PACKAGE 74ACT16833 . . . DL PACKAGE

(TOP VIEW)

1OEB 1 1CLK 2 1ERR 3 GND 4

1A1 5 1A2 6 VCC 7 1A3 8 1A4 9 1A5 10 GND 11 1A6 12 1A7 13 1A8 14 2A1 15 2A2 16 2A3 17 GND 18 2A4 19 2A5 20 2A6 21 VCC 22 2A7 23 2A8 24 GND 25 2ERR 26 2CLK 27 2OEB 28

56 1OEA 55 1CLR 54 1PARITY 53 GND 52 1B1 51 1B2 50 VCC 49 1B3 48 1B4 47 1B5 46 GND 45 1B6 44 1B7 43 1B8 42 2B1 41 2B2 40 2B3 39 GND 38 2B4 37 2B5 36 2B6 35 VCC 34 2B7 33 2B8 32 GND 31 2PARITY 30 2CLR 29 2OEA

The error (1ERR or 2ERR) output is configured as an open-collector output. The B-to-A parity error flag is clocked into 1ERR or 2ERR on the low-to-high transition of the clock (1CLK or 2CLK) input. 1ERR or 2ERR is cleared (set high) by taking the clear (1CLR or 2CLR) input...